## FLOPPY DISK WRITE CONTROLLER/HEAD DRIVER

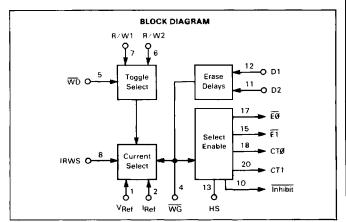

The MC3471 is a monolithic integrated Write Controller/Head Driver designed to provide the entire interface between the write data and head control signals and the heads (write and erase) for either Tunnel or straddle-erase floppy disk systems.

Provisions are made for selecting a range of accurately controlled write currents and for head selection during both read and write operation. Additionally, provisions are included for externally adjusting degauss period, inner/outer track compensation, and the delay from write gate to erase turn-on and turn-off.

Erase Delays are controlled by driving the delay inputs D1 and D2 with standard TTL open-collector logic (microprocessor compatible) or by using the external RC mode in which case the delay is one  $\tau$  (K factor = 1.0).

In addition, an Inhibit output is provided which indicates that the heads are active during write, degauss, or erase.

- Head Selection Current Steering Through Write Head and Erase Coil in Write Mode

- Adjustable On-Chip Delay of Erase Timing Stable K Factor

- Delay Pins Logic Compatible for Direct Microprocessor Compatibility

- Inhibit Output Provided to Disable Read or Step During Head Active Time

- Provides High Impedance (Read Data Enable) During Read Mode

- Head Current (Write) Guaranteed  $\pm\,3\%$  (3.0 mA using Rext = 10 k\Omega)

- IRW Select Input Provides for Inner/Outer Track Compensation

- Degauss Period Externally Adjustable

- Specified With Head Supply (VBB) from 10.8 V to 26.4 V

- Minimizes External Components

- See Application Note AN917 for Further Information

# FLOPPY DISK WRITE CONTROLLER (WITH ERASE DELAY)

SILICON MONOLITHIC INTEGRATED CIRCUIT

7

# 7/

# MAXIMUM RATINGS (TA = 25°C)

| Rating                               | Symbol           | Value       | Unit |  |

|--------------------------------------|------------------|-------------|------|--|

| Power Supply Voltage (Pin 14)        | Vcc              | 7.0         | Vdc  |  |

| Power Supply Voltage (Pin 19)        | VBB              | 30          | Vdc  |  |

| Input Voltage (Pins 4, 5, 8, 13)     | VI               | 5 75        | Vdc  |  |

| Output Applied Voltage (Pin 10)      | v <sub>o</sub>   | 7.0         | Vdc  |  |

| Open-Collector Sink Current (Pin 10) | 10               | 25          | mA   |  |

| Storage Temperature                  | T <sub>stg</sub> | -55 to +150 | °C   |  |

| Operating Junction Temperature       | TJ               | 150         | °C   |  |

# **RECOMMENDED OPERATING CONDITIONS**

| Rating                              | Symbol | Value          | Unit |  |

|-------------------------------------|--------|----------------|------|--|

| Power Supply Voltage (Pin 14)       | Vcc    | +4.75 to +5.25 | Vdc  |  |

| Power Supply Voltage (Pin 19)       | VBB    | +10.8 to +26.4 | Vdc  |  |

| Operating Ambient Temperature Range | TA     | 0 to +70       | "C   |  |

**ELECTRICAL CHARACTERISTICS** ( $T_A$  = 0 to +70°C,  $V_{CC}$  = 4.75 to 5.25 V.  $V_{BB}$  = 10.8 to 26.4 V unless otherwise noted. Typicals given for  $V_{CC}$  = 5.0 V.  $V_{BB}$  = 12 V and  $T_A$  = 25°C unless otherwise noted.)

| Characteristics                                                                                                              | Pins        | Symbol            | Min        | Тур          | Max      | Unit |

|------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------|------------|--------------|----------|------|

| DIGITAL INPUT VOLTAGES                                                                                                       |             |                   |            | •——          |          |      |

| Power Supply Current — V <sub>CC</sub> V <sub>BB</sub>                                                                       |             | I <sub>CC</sub>   |            | 22<br>15     | 60<br>30 | mA   |

| High Level Input Voltage<br>(V <sub>CC</sub> = 4.75 V)                                                                       | 4, 8, 13    | VIH               | 2.0        |              | _        | ٧    |

| Low Level Input Voltage<br>(VCC = 5.25 V)                                                                                    | 4, 8, 13    | VIL               | -          | _            | 0.8      | ٧    |

| Input Clamp Voltage<br>(I <sub>IK</sub> = -12 mA)                                                                            | 4, 5, 8, 13 | VIK               |            | -0.87        | -1.5     | ٧    |

| Positive Threshold (V <sub>CC</sub> = 5.0)                                                                                   | 5           | ∨ <sub>T(+)</sub> | 1.5        | 1.75         | 2.0      | V    |

| Negative Threshold (V <sub>CC</sub> = 5.0)                                                                                   | 5           | ∨ <sub>T(−}</sub> | 0.7        | 0.98         | 1.3      | ٧    |

| Hysteresis (VT(+) - VT(-)) TA = 0°C to +70°C TA = 25°C                                                                       | 5           | VHTS              | 0.2<br>0.4 | 0.76         |          |      |

| DIGITAL INPUT CURRENTS                                                                                                       |             |                   |            |              |          |      |

| High Level Input Current<br>(V <sub>CC</sub> = 5.25 V, V <sub>BB</sub> = 26.4 V, V <sub>I</sub> = 2.4 V)                     | 4, 5, 8, 13 | ЧН                | _          | 0.1          | 40       | μА   |

| Low Level Input Current<br>(V <sub>CC</sub> = 5.25 V, V <sub>BB</sub> = 26.4 V, T <sub>A</sub> = 25°C unless<br>noted below) | 4, 5, 8, 13 | կլ                |            |              | -1.6     | mA   |

| V <sub>BB</sub> = 12 V                                                                                                       | 4           |                   | _          | 0.36<br>0.76 | -        |      |

| V <sub>BB</sub> = 24 V<br>V <sub>CC</sub> = 5.0 V                                                                            | 5           |                   | _          | 0.46         | _        |      |

| $V_{CC} = 5.0 \text{ V}$                                                                                                     | 8, 13       |                   | _          | 0.39         | _        |      |

**ELECTRICAL CHARACTERISTICS (continued)** ( $T_A=0$  to  $+70^{\circ}$ C,  $V_{CC}=4.75$  to 5.25 V,  $V_{BB}=10.8$  to 26.4 V unless otherwise noted. Typicals given for  $V_{CC}=5.0$  V,  $V_{BB}=12$  V and  $T_A=25^{\circ}$ C unless otherwise noted.)

| Characteristics                                                                                                                                                    | Pins   | Symbol            | Min                  | Тур                 | Max            | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------|----------------------|---------------------|----------------|------|

| CENTER-TAP and ERASE OUTPUTS                                                                                                                                       |        |                   |                      |                     |                |      |

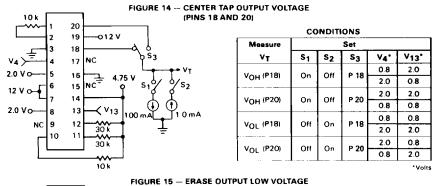

| Output High Voltage (See Figure 14)<br>(I <sub>OH</sub> = -100 mA, V <sub>CC</sub> = 4.75 V)<br>V <sub>BB</sub> = 10.8 to 26.4 V                                   | 18, 20 | Voн               | V <sub>BB</sub> -1.5 | V <sub>BB</sub> ·10 |                | V    |

| Output Low Voltage (See Figure 14) (IOL = 1.0 mA) VBB = 12 V                                                                                                       | 18. 20 | VOL               | -                    | 70                  | 150            | m∨   |

| V <sub>BB</sub> = 24 V                                                                                                                                             | 15, 17 | la.               | -                    | 70<br>0.01          | 150            |      |

| Output High Leakage Current<br>(VOH = 24 V, V <sub>CC</sub> = 4.75 V, V <sub>BB</sub> = 24 V)                                                                      |        | Юн                |                      | 0.01                |                | μΑ   |

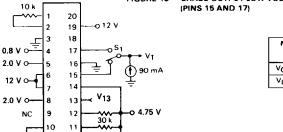

| Output Low Voltage (See Figure 15) (IOL = 90 mA, V <sub>CC</sub> = 4.75 V) V <sub>BB</sub> = 12 V                                                                  | 15, 17 | VOL               |                      | 027                 | 0 60           | ٧    |

| V <sub>BB</sub> = 24 V                                                                                                                                             |        |                   | -                    | 027                 | 0 60           |      |

| DIGITAL OUTPUT LEVEL (Inhibit)                                                                                                                                     |        |                   |                      |                     |                |      |

| High Level Output Current<br>(VOH = 7.0 V, VCC = 4.75 V)                                                                                                           | 10     | ф                 | <u>-</u>             | _                   | 100            | μА   |

| Low Level Output Voltage<br>(IOL = 4.0 mA, VCC = 4.75 V)                                                                                                           | 10     | VOL               | _                    |                     | 05             | V    |

| CURRENT SOURCE                                                                                                                                                     |        |                   |                      |                     |                |      |

| Reference Voltage                                                                                                                                                  | 1      | ·V <sub>Ref</sub> | -                    | 57                  |                | V    |

| Degauss Voltage (See Text)<br>(Voltage Pin 1 - Voltage Pin 2)                                                                                                      | 1      | V <sub>DEG</sub>  | =                    | 10                  | _              | ٧    |

| Bias Voltage                                                                                                                                                       | 2      | V <sub>F</sub>    | -                    | 0.7                 | _              | ٧    |

| Write Current Off Leakage<br>(V <sub>OH</sub> = 30 V)                                                                                                              | 6, 7   | <sub>Г</sub> он   |                      | 0 03                | 15             | μΑ   |

| Saturation Voltage<br>(VBB = 12 V)                                                                                                                                 | 6, 7   | V <sub>sat</sub>  | -                    | 0.85                | 2.7            | V    |

| Current Sink Compliance<br>(For V <sub>6, 7</sub> = 4.0 V to 24 V, V <del>WG</del> = 0.8 V)                                                                        | 6, 7   | ∆I/RW2, 1         |                      | 15                  | 40             | μА   |

| Average Value Write Current $ \frac{(\frac{1 \text{Pin } 6 + \frac{1 \text{Pin } 7}{2}}{2} \text{ for V}_{BB} = 10.8 \text{ to } 26.4 \text{ V} ) }{2} $           | 6, 7   |                   |                      |                     |                |      |

| @ I <sub>R/W</sub> = I <sub>LOW</sub> , R = 10 k<br>T <sub>A</sub> = 25°C<br>T <sub>A</sub> = 0 to +70°C<br>@ I <sub>R/W</sub> = I <sub>LOW</sub> , R = 5.0 k      |        | FR/W(L)           | 2.91<br>2.84         | 3.0                 | 3.09<br>3.16   | mΔ   |

| T <sub>A</sub> = 25°C<br>T <sub>A</sub> = 0 to +70°C                                                                                                               |        | 1                 | 5.64<br>5.51         | 5.89<br>—           | 6.14<br>6.28   | n/   |

| @ I <sub>R/W</sub> = I <sub>HI</sub> , R = 10 k (I <sub>HI</sub> = I <sub>LOW</sub> + % I <sub>LOW</sub> )<br>T <sub>A</sub> = 25°C<br>T <sub>A</sub> = 0 to +70°C |        | ΔIR/W(H)          | 31 3<br>30 3         | 33.3<br>33.3        | 35.5<br>36.6   | %    |

| Difference in Write Current<br>(I)Pin 6 - IPin 7I<br>@ IR/W = I <sub>LOW</sub> , V <sub>BB</sub> = 10.8 V to 26.4 V)<br>R = 10 k                                   | 6, 7   | lR/W7             |                      |                     |                | mA   |

| T <sub>A</sub> = 25°C<br>T <sub>A</sub> = 0 to +70°C<br>R = 5.0 k                                                                                                  |        |                   | _<br>_               | 0.003               | 0.015<br>0.023 |      |

| T <sub>A</sub> = 25°C<br>T <sub>A</sub> = 0 to +70°C                                                                                                               |        |                   | _                    | _                   | 0.030<br>0.046 |      |

ERASE DELAY ACCURACY (V<sub>CC</sub> = 4.75 to 5.25 V, T<sub>A</sub> = 0 to +70°C, V<sub>BB</sub> = 10.8 to 26.4 V, — refer to Figure 9.)

| Characteristics                                                                                                          | Test              | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------------------------------------------------------|-------------------|-----|-----|-----|------|

| Delay Error, Pin 11, 12<br>D1, D2 = RC $\pm$ E <sub>D1, 2</sub> , 30 k $\Omega$ $\leqslant$ R $\leqslant$ 300 k $\Omega$ | E <sub>D1,2</sub> | -   | -   | 15  | %    |

# AC SWITCHING CHARACTERISTICS (V<sub>CC</sub> = 5.0 V, $T_A$ = 25°C, $V_{BB}$ = 24 V, $I_{RWS}$ = 0.4 and $I_{R/W}$ = 3.0 mA unless otherwise noted.)

| Characteristics (Note 1)                                                                                                         | f <sub>in</sub> (Note 2) | Min | Тур  | Max | Unit |

|----------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----|------|-----|------|

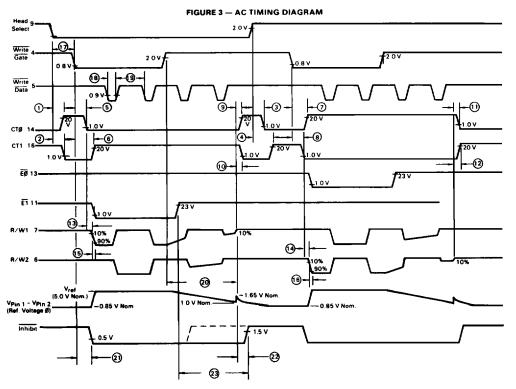

| <ol> <li>Delay from Head Select going low through 0.8 V to CT0<br/>going high through 20 V.</li> </ol>                           | HS, Pin 13               |     | 1.6  | 4.0 | μs   |

| Delay from Head Select going low through 0.8 V to CT1 going low through 1.0 V.                                                   | HS, Pin 13               | 1   | 2.1  | 4.0 | μs   |

| <ol><li>Delay from Head Select going high through 2.0 V to CT0<br/>going low through 1.0 V.</li></ol>                            | HS, Pin 13               |     | 1.7  | 4.0 | μς   |

| <ol> <li>Delay from Head Select going high through 2.0 V to CT1<br/>going high through 20 V.</li> </ol>                          |                          | -   | 1.4  | 4.0 | μs   |

| Delay from WG going low through 0.8 V to CTO going low through 1.0 V.                                                            | WG, Pin 4                | _   | 1.3  | 4.0 | μs   |

| Delay from WG going low through 0.8 V to CT1 going high through 20 V.                                                            | WG, Pin 4                |     | 0.8  | 4.0 | μs   |

| Delay from WG going low through 0.8 V to CTO going high through 20 V.                                                            | WG, Pin 4                | -   | 0.75 | 4.0 | μS   |

| 8. Delay from WG going low through 0.8 V to CT1 going low through 1.0 V.                                                         | WG, Pin 4                | -   | 1.2  | 40  | μ5   |

| <ol> <li>After WG goes high, delay from R/W1 turning off<br/>through 10% to CTØ going high through 20 V.</li> </ol>              | WG, Pin 4                | 20  | 750  | -   | ns   |

| <ol> <li>After WG goes high, delay from R/W1 turning off<br/>through 10% to CT1 going low through 1.0 V.</li> </ol>              | WG, Pin 4                | 20  | 1200 |     | ns   |

| 11. After WG goes high, delay from R/W2 turning off through 10% to CT0 going low through 1.0 V.                                  | WG, Pin 4                | 20  | 1200 |     | ns   |

| 12. After WG goes high, delay from R ∕ W2 turning off through 10% to CT1 going high through 20 V                                 | WG, Pin 4                | 20  | 600  | -   | ns   |

| <ol> <li>After WG goes low, delay from CTØ going low through<br/>1.0 V to R/W1 turning on through 10%.</li> </ol>                | WG, Pin 4                | 20  | 750  | _   | ns   |

| <ol> <li>After WG goes low, delay from CT1 going low through<br/>1.0 V to R/W2 turning on through 10%.</li> </ol>                | WG, Pin 4                | 20  | 750  | _   | ns   |

| 15. After WG goes low, fall time (10% to 90%) of R/W1.                                                                           | WG, Pin 4                |     | 5.0  | 200 | ns   |

| 16. After WG goes low, fall time (10% to 90%) of R/W2.                                                                           | WG, Pin 4                | -   | 5.0  | 200 | ns   |

| Setup time, Head Select going low before     WG going low.                                                                       | WG, Pin 4                | 4.0 |      | -   | μs   |

| 18. Write Data low Hold Time                                                                                                     | WD, Pin 5                | 200 |      | _   | ns   |

| 19 Write Data high Hold Time                                                                                                     | WD, Pin 5                | 500 |      |     | ns   |

| Delay from WG going high through 2.0 V     to R/W 1 turning off through 10% of on value.                                         | WG, Pin 4                | _   | 3.9  | _   | μ\$  |

| 21. Delay from WG going low thru 0.8 V<br>to Inhibit going low thru 0.5 V                                                        | WG, Pin 4                | _   | 0.08 | 4.0 | μs   |

| After WG goes high, delay from R/W1 turning off<br>thru 10% to inhibit going high thru 1.5 V (10 k pullup<br>on Inhibit, Note 3) | WG, Pin 4                | 20  | 750  | -   | ns   |

| 23. After WG goes high, delay from ET going high thru 23 V to Inhibit going high thru 1.5 V (10 k pullup on Inhibit, Note 3)     | WG                       | 20  | 750  | _   | ns   |

Notes:

1. Test numbers refer to encircled numbers in Figures 3 & 16.

2. AC test waveforms applied to the designated pins as follows:

fin Amplitude **Duty Cycle**

HS. Pin 13 WG, Pin 4 WD, Pin 5 50 kHz 50 kHz 1.0 MHz 0.4 to 2.4 V 0.4 to 2.4 V 0.2 to 2.4 V 50% 50% 50%

<sup>3.</sup> Test Conditions 22, or 23, whichever produces the longer delay, will control inhibit.

AC SWITCHING CHARACTERISTICS (continued) ( $V_{CC}$  = 5.0 V,  $T_A$  = 25°C,  $V_{BB}$  = 24 V,  $\overline{WG}$  = 0.4 unless otherwise noted)

| Characteristics (Note 4)                                                                                                          | Min | Тур | Max | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

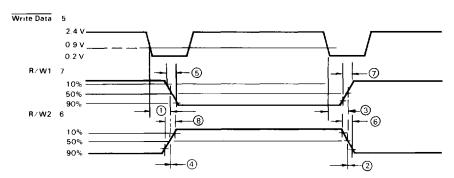

| Delay from Write Data going low through 0.9 V to R/W1 turning on through 50%.                                                     | _   | 85  | -   | ns   |

| Delay skew, difference of R/W1 <u>turning off</u> and R/W2<br>turning on through 50% after Write Data going low<br>through 0.9 V. | _   | 1,0 | ±40 | ns   |

| Delay from Write Data going low through 0.9 V to R/W1 turning off through 50%.                                                    | _   | 80  | _   | ns   |

| Delay skew, difference of R/W1 turning on and R/W2 turning off 50% after Write Data going low through 0.9 V.                      | -   | 1.0 | ±40 | ns   |

| 5 Fall time, 10% to 90%, of R/W1                                                                                                  |     | 1.7 | 200 | ns   |

| 6. Fall time, 10% to 90%, of R/W2                                                                                                 |     | 1.7 | 200 | ns   |

| 7. Rise time, 90% to 10%, of R/W1                                                                                                 |     | 12  | 200 | ns   |

| 8. Rise time, 90% to 10%, of R/W2                                                                                                 |     | 12  | 200 | ns   |

Note 4. Test numbers refer to encircled numbers in Figures 2 & 15.  $f_{\text{In}} = 1.0 \; \text{MHz}, 50\% \; \text{Duty Cycle and Amplitude of 0.2 V to 2.4 V}.$

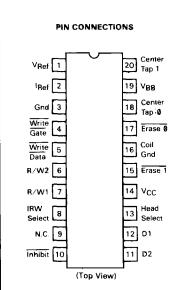

# PIN DESCRIPTION TABLE

| Name             | Symbol           | Pin | Description                                                                                                                                                                                                                    |

|------------------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Head Select      | HS               | 13  | Head Select input selects between the head I/O pins; center-tap, erase, and read/write. A HIGH selects Head 0 and a LOW selects Head 1.                                                                                        |

| Write Gate       | WG               | 4   | Write Gate input selects the mode of operation. HIGH selects the read mode, while LOW selects the Write Control mode and forces the write current                                                                              |

| Write Data       | ₩D               | 5   | Write Data input controls the turn on / off of the write current. The internal divide-by-two flip-flop toggles on the negative going edge of this input to direct the current alternately to the two halves of the head coils. |

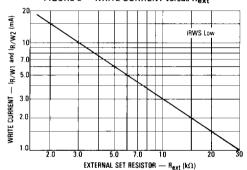

| IRW Select       | IRWS             | 8   | IRW Select input selects the amount of write current to be used. When LOW, the current equals the value found in Figure 5, according to the external resistor. When HIGH, the current equals the low current + 33%.            |

| V <sub>Ref</sub> | V <sub>Ref</sub> | 1 2 | A resistor between these pins sets the write current. (Refer to Figure 4.) A capacitor from $V_{\mbox{Ref}}$ to Gnd will adjust the Degauss period.                                                                            |

| Center-Tap 0     | СТØ              | 18  | Center-Tap 0 output is connected to the center tap of Head 0. It will be pulled to Gnd or VBB (+12 or +24) depending on mode and head selection.                                                                               |

| Erase 0          | ĒΟ               | 17  | Erase Ø will be LOW for writing on Head Ø, and floating for other conditions.                                                                                                                                                  |

| Center-Tap 1     | CT1              | 20  | Center-Tap 1 output is connected to the center tap of Head 1. It will be pulled to Gnd or VBB (+12 or +24) depending on mode and head selection.                                                                               |

| Erase 1          | Ēī               | 15  | Erase 1 will be LOW for writing on Head 1, and floating for other conditions.                                                                                                                                                  |

| R/W2             | R/W2             | 6   | R/W2 input is one of the differential inputs that sinks current during writing, being the opposite phase of R/W1. It will be connected to one side of the heads.                                                               |

| R/W1             | R/W1             | 7   | R/W1 input is one of the differential inputs that sinks current during writing, being the opposite phase of R/W2. It will be connected to one side of the heads.                                                               |

|                  | Vcc              | 14  | +5.0 V Power                                                                                                                                                                                                                   |

|                  | VBB              | 19  | +12 V or + 24 V Power                                                                                                                                                                                                          |

|                  | Gnd              | 16  | Coil grounds                                                                                                                                                                                                                   |

|                  | Gnd              | 3   | Reference and logic ground                                                                                                                                                                                                     |

| Delay 1          | D1               | 12  | Erase Turn-On Delay adjust (RC or Logic)                                                                                                                                                                                       |

| Delay 2          | D2               | 11  | Erase Turn-Off Delay adjust (RC or Logic)                                                                                                                                                                                      |

| Inhibit          | Inhibit          | 10  | Active low open-collector output provided to indicate heads are active in the write, degauss or erase mode. (Used for step or read inhibit.)                                                                                   |

|                  |                  | _   |                                                                                                                                                                                                                                |

### FIGURE 1 - LOGIC DIAGRAM

FIGURE 2 - R/W1 AND R/W2 RELATIONSHIP

# MC3471

# 7

### **APPLICATION INFORMATION**

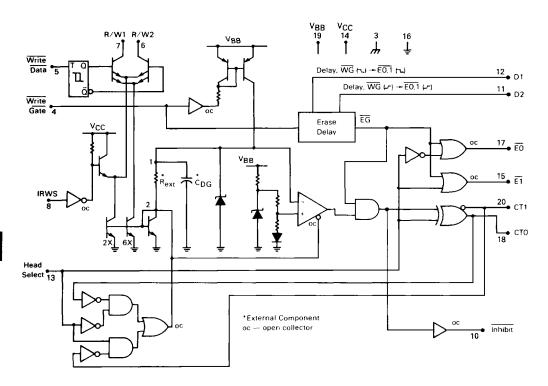

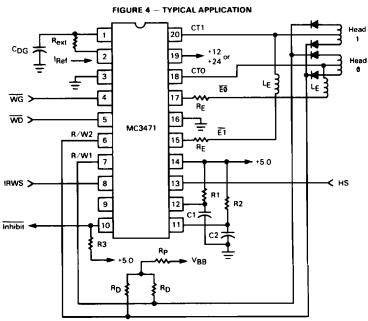

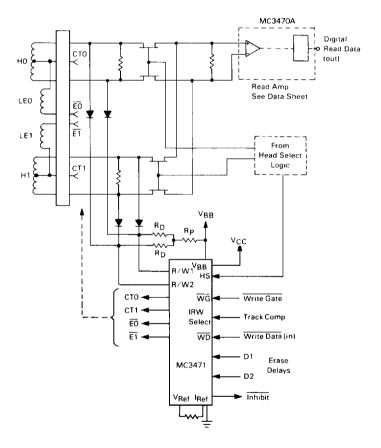

The MC3471P serves as a complete interface between the Write Control functional signals (Head Select, Write Data, Write Gate and inner track compensation, IRWS) and the head itself. A typical configuration is shown in Figure 4. Lg's are erase coils.

#### WRITE CURRENT SELECTION

Although the MC3471P has been specified for 3.0 mA write current (with a 10 k $\Omega$  external resistor), a range of write current values can be chosen by varying  $R_{\text{ext}}$  using the plot in Figure 5. This current can also be derived using

the relationship

$$I_{Write}$$

(mA) =  $\frac{30}{R_{ext}(k\Omega)}$

$I_{Ref}$ , the current flowing in  $R_{ext}$  (required only for dissipation calculations) can be worst case using the fact that the differential voltage between Pins 1 and 2 ( $V_{Ref}$ ) shown in Figure 3 never exceeds 5.0 volts. With a low value of  $R_{ext} = 1.0 \ k\Omega$ ,  $P_D = 25 \ mW$ .

FIGURE 5 - WRITE CURRENT versus Rext

#### WRITE CURRENT DAMPING

Referring to Figure 4, resistors R<sub>D</sub> are used to dampen any ringing that results from applying the relatively fast risetime write current pulse to the inductive head load. Values chosen will be a function of head characteristics and the desired damping. Rp serves as a common pullup resistor to the head supply V<sub>RB</sub>.

### **DEGAUSS PERIOD**

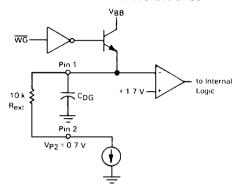

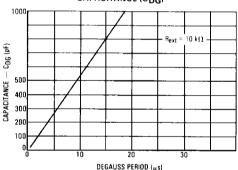

Degauss of the read/write head can be accomplished at the end of each write operation by attaching a capacitor from Pin 1 to ground. The time relationship that results is shown in Figure 7. A simplified diagram of this function is shown in Figure 6.

While  $\overline{WG}$  is low, the selected write current flows into Pin 6 or Pin 7 (R/W1) or R/W2) and is mirrored through the external resistor,  $R_{ext}$ . The degauss capacitor,  $C_{DG}$ , will be charged to approximately 5.7 volts. After  $\overline{WG}$  goes high, the voltage on  $C_{DG}$  begins to decay toward 0.7 V. When the voltage reaches the comparator threshold of 1.7 V, the comparator output triggers the internal logic to completely turn off the write current. At this point, the pulse amplitude on the R/W1 and R/W2 pins has returned to 10% of its maximum value.

Figure 7. Degauss Period shows the relationship between  $C_{DG}$  and Degauss Period for  $R_{ext}$  =  $10 \text{ k}\Omega$ . This period is equal to the exponential delay time for the voltage as mentioned plus internal delay times.

FIGURE 6 - SIMPLIFIED DEGAUSS CIRCUIT

FIGURE 7 — DEGAUSS PERIOD versus CAPACITANCE (CDG)

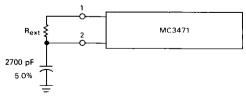

### POWER-UP WRITE CURRENT CONTROL

During power-up, under certain conditions (VBB comes up first while  $\overline{WG}$  is low), there can be a write current transient on Pins 6 and 7 (R/W1 and R/W2) of sufficient magnitude to cause writing to occur if the head is loaded.

This transient can be eliminated by placing a capacitor from Pin 2 to ground. This also delays the write current when  $\overline{WG}$  goes low and this delay must be accounted for when the capacitor on Pin 2 is used. The delay is 3.0  $\mu s$  for a 2700 pF capacitor, and  $R_{ext} = 10 \text{ k}\Omega$ . Values up to 7000 pF may be used.

See Application Note AN917 for further information.

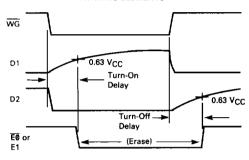

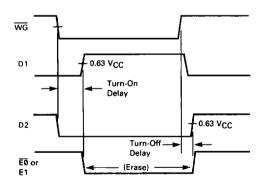

#### **ERASE DELAY**

The MC3471P can be used with both straddle and tunnel erase heads. When using the tunnel erase heads, it is necessary to delay the erase current in time with respect to WG due to the physical placement of the erase gap behind the R/W gap on the heads. The amount of delay required depends upon the disk rotation velocity, recording density and format. Turn-on delay and turn-off delay must also be independent to guarantee erase is on for the entire block.

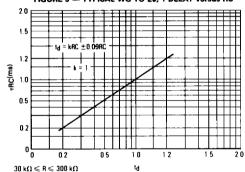

Nominal delays of 500  $\mu$ s turn-on; and 1.0 ms turn-off are available by adjusting the value of R1, R2 and C1, C2 shown in Figure 4. These delays are adjustable over a broad range as shown in Figure 9 to achieve any practical delay required. By using 5% capacitors and 1% resistors, total timing accuracy is better than  $\pm$  15% over temperature and supply. Timing is shown in Figure 10.

In applications using logic or microprocessor controlled delays, the D1 and D2 inputs can be used directly to turn-on and turn-off the erase current. (Controlling outputs should be Open-collector w/10 k pullup). Figure 11 shows the relative timing involved for the microprocessor and logic controlled applications.

In straddle erase systems, the erase delays can be eliminated by pulling D1 and D2 high thru a 10  $k\Omega$  pullup resistor to +5.0 V.

FIGURE 9 - TYPICAL WG TO E8, 1 DELAY versus RC

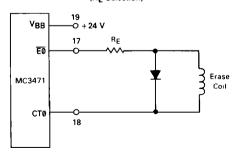

#### **ERASE CURRENT**

The value of R<sub>E</sub>, the erase current set resistor, is found by referring to Figure 12 and selecting the desired erase current.

Looking at the simplified erase current path in Figure 12, when writing, CTØ will be high (VOH(min) = 22.5 V) and EØ will be low (VOL(max) = 0.6 V). If the erase coil resistance is 10  $\Omega$  and 40 mA of erase current is desired then:

$$(R_E + 10 \Omega) \times 40 \text{ mA} = (22.5 - 0.6) \text{ V}$$

or

$$R_E = \frac{21.9 \text{ V}}{0.04 \text{ A}} - 10 \Omega = 537 \Omega$$

$$P_D = (537) (0.04)^2 = 0.86 W$$

This gives the minimum value  $R_E$  for worst case  $V_{OH}/V_{OL}$  conditions. It is also recommended that a diode be used as indicated for inductive back emf suppression.

FIGURE 10 — DELAY INPUT FUNCTION/TIMING WITH RC ELEMENTS

FIGURE 11 -- DELAY INPUT FUNCTION/TIMING WITH LOGIC CONTROL

FIGURE 12 — ERASE CURRENT (RF Selection)

7

FIGURE 13 — TYPICAL DUAL HEAD FLOPPY DISK SYSTEM USING FET GATE READ CHANNEL SELECTION AND MC3471/MC3470A

| Function | СТ●             | CT1 | EØ  | E1  |

|----------|-----------------|-----|-----|-----|

| Write 0  | VBB             | 0 V | On  | Off |

| Write 1  | 0 V             | VBB | Off | On  |

| Read 0   | 0 V             | VBB | Off | Off |

| Read 1   | V <sub>BB</sub> | 0 V | Off | Off |

# **TEST FIGURES**

30 k

Weasure

Set

Vγ

S1

V13

VOL (P15)

P15

0.8V

VOL (P17)

P17

2.0 V

Tunnel Erase S1 and S4 Open S2, S3 Closed

CONDITIONS

FIGURE 16 - TIMING TEST CIRCUIT 10 k +5.0 V ±5% +24 V ±5% 100 Vcc ٧вв 10 Inhibit 1 2 k CT0 Write Data 20 ₹ 240 \$ 2.0 W 240 Write Gate 2.0 W 17 AC ΕŌ 270 2.0W Inputs 13 Head Select +24 V 270 2.0 W 125 k 50 IRW Select R/W 301 30 k (0.1%) (0.1%)50 R/W2 S2 ~ 11 D2  $v_{\text{Ref}}$ **₹10 k (0.1%)**. <sup>I</sup>Ref Diodes Type 1N4934 4000 pF 8000 pF Resistors (unless otherwise noted) are 1/4 W 5% 200 pF 3, 16 (0.1%)(0.1%)Straddle Erase S1 and S4 Closed \$2, \$3 Open

7